vlsi testing white papers|vlsi problems and solutions : China Abstract Very-large-scale integration (VLSI) testing encompasses all spectrums of test methods and structures embedded in a system-on-chip (SOC) to ensure the quality of .

WEB30 de ago. de 2023 · De acordo com as reflexões cristãs sobre a música “O Crente Quando Chora O Senhor Responde”, existem várias promessas de consolo e resposta divina que são mencionadas nas escrituras sagradas. Essas promessas são fontes de esperança e encorajamento para os crentes que passam por momentos de tristeza, .

{plog:ftitle_list}

Japan - Soccer Live Scores 2in1 Odds,Macao Asia Odds,Sta.

We analyze the challenges associated with traditional VLSI testing techniques and showcase how ML algorithms are increasingly being employed to enhance fault detection, diagnosis, and .

This paper first reviews the basics of VLSI testing, focusing on test generation and design for testability. Then it discusses the impact of test power in scan testing, and highlights .

2021 IEEE 39th VLSI Test Symposium (VTS 2021) (Table of Contents) Virtual Conference 25 – 28 April 2021. IEEE Catalog Number: ISBN: CFP21029-POD. 978-1-6654-3005-0 Copyright © .

The phenomenal development in electronic systems has, in large part, the advances in Very Large Scale of Integration (VLSI) semiconductor technologies to thank. .

A Hardware-Based Evolutionary Algorithm with Multi-Objective Optimization Operators for On-. Chip Transient Fault Detection .

Abstract Very-large-scale integration (VLSI) testing encompasses all spectrums of test methods and structures embedded in a system-on-chip (SOC) to ensure the quality of .Explore the latest full-text research PDFs, articles, conference papers, preprints and more on VLSI TESTING. Find methods information, sources, references or conduct a literature review .VLSI TEST PRINCIPLES AND ARCHITECTURES. The rapid growth of silicon technology and the demands of applications are increasingly forcing electronics designers to take a systems . Several Electronic Design Automation tools for fault identification and test pattern development are available to simulate circuits for structural testing. This chapter gives a brief .

The article provides an overview of key ML applications in VLSI testing, including anomaly detection, and adaptive testing strategies, and concludes by illuminating the integration of ML techniques in addressing the escalating complexities of modern semiconductor devices and the potential future directions and emerging trends. The semiconductor industry’s relentless . The current research in VLSI explores emerging trends and novel ideas and concepts covering a broad range of topics in the area of VLSI: from VLSI circuits, systems, and design methods, to system-level design and systemon- chip issues, to bringing VLSI methods to new areas and technologies such as nano and molecular devices, MEMS, and quantum . VLSI, an acronym for Very Large Scale Integration is a technology to place thousands (even more) of electronic components onto a single chip. Currently VLSI architecture is employed everywhere in electronic devices such that TV, computer, laptop and mobile phones. VLSI design comprises of Front End Design and Back End design. While front end.

His research interests include Digital Design, Embedded Systems, System-on-Chip (SoC) and Network-on-Chip (NoC) Design and Test, Power- and Thermal-aware Testing of VLSI Circuits and Systems. He has published more than 150 papers . The BIST has become a promising solution to VLSI testing problems and has been widely used in industry. . Synopsys White Paper, 2010. Google Scholar D. B. Armstrong, “A Deductive Method for Simulating Faults in Logic Circuits”, in IEEE Trans. on Computers, vol. C-21, no. 5, pp. 464–471, 1972. Google . As the compactness of VLSI circuits increase, it becomes striking to integrate devoted test logic on a chip. Starting with a general idea of test problems, this survey paper reviews test applications and its terms, common test methods and analyzes the basic test procedure. The concept of Built-in Self-Test (BIST) is introduced and discussed, incentives .5 Books Essential of Electronic Testing for Digital, Memory, and Mixed Signal VLSI Circuits Michel.L. Bushnell and Vishwani D. Agrawal Springer 2005 Logic Testing and Design for Testability Hideo Fujiwara MIT Press 1985 Digital System Testing and Testable Design M. Abramovici, M. Breuer, A. Friedman IEEE Press 1994 (now available in Jayco Publication)

Download Latest MTech VTU VLSI Testing of 1st semester VLSI DESIGN AND EMBEDDED SYSTEMS with subject code 20EVE14 2020 scheme Question Papers. . VTU VLSI Testing MAR 2022 Question Paper Download VTU 20EVE14 Mar 2022 MTech paper. Last Updated: Monday, February 13, 2023. Categories. VTU Time Table New; VTU Model .

hardness teste

In the field of VLSI testing, time-to-market and production costs are critical factors that directly impact the profitability and competitiveness of semiconductor companies. Machine Learning (ML) has emerged as a powerful tool for accelerating test time and reducing costs, offering significant advantages over traditional testing methods. .

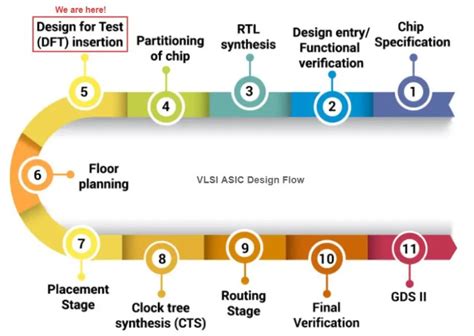

VLSI Testing Trends and Advancements. As technology continues to advance, new trends and advancements in VLSI testing are emerging. Some of these include: Design for Testability (DFT) DFT is an approach that involves designing circuits with built-in testability features. These features facilitate the testing process by providing easy access to .Voted Best Paper 3rd Place: SNUG 2019 (Silicon Valley) Finite State Machine (FSM) Deisgn & Synthesis using SystemVerilog - Part I Rev 1.0 Feb 2019: Voted Best Paper 1st Place: SNUG 2018 (Austin) UVM Analysis Port Functionality and Using Transaction Copy Commands Rev 1.0 Oct 2018: Voted Best Paper 2nd Place: SNUG 2018 (Silicon Valley)

vlsi testing technology

VLSI Test Principles and Architectures Ch. 8-Memory Testing &BIST -P. 8 Static RAM Fault Models: SAF/TF Stuck-At Fault (SAF) Cell (line) SA0 or SA1 – A stuck-at fault (SAF) occurs when the value of a cell or line is always 0 (a stuck-at-0 fault) or always 1 (a stuck-at-1 fault). – A test that detects all SAFs guarantees that from each Feature papers represent the most advanced research with significant potential for high impact in the field. A Feature Paper should be a substantial original Article that involves several techniques or approaches, provides an outlook for future research directions and describes possible research applications. . VLSI Design, Testing, and .Explore the latest full-text research PDFs, articles, conference papers, preprints and more on VLSI TESTING. Find methods information, sources, references or conduct a literature review on VLSI .

In this paper, we present a survey of the low power testing techniques that can be used to test VLSI systems. In the first part, the paper explains the problems induced by the increased power consumed during functional testing of a circuit, in either external testing or .The VTS Program Committee invites original, unpublished, and not currently under review paper submissions for VTS 2021, in the following categories.. SCIENTIFIC PAPERS. Complete manuscripts, up to six pages (the references do not count towards the page limit) in a standard IEEE two-column format (10pt).Papers exceeding the page limit will be returned without review. Testing verifies a circuit's accuracy regarding gates and connections between them. The fundamental purpose of testing is to model the circuit's various activities. Several Electronic Design Automation tools for fault identification and test pattern development are available to simulate circuits for structural testing. 5. Interpret testing and testability issues in VLSI Design . Question paper pattern: Examination will be conducted for 100 marks with question paper containing 10 full questions, each of 20 marks. Each full question can have a maximum of 4 sub questions. There will be 2 full questions from each module covering all the topics of the module.

Question Paper Code: 71872 M.E. DEGREE EXAMINATION,JUNE/JULY 2013. Elective VLSI Design VL9251/VL951/10244 VLE 22- TESTING OF VLSI CIRCUITS (Reg ilation 2009/2010) Time: Three hours Maximum: 100marks Answer ALLquestions. PARTA- (10 x 2= 20 marks) 1. Draw a possible model for compiled simulation for the given Latch.The over-voltage stress test is set-up to determine the ability of the power supplies to withstand transient voltages. For digital products, each input condition (high and low) must be checked by the over-voltage test. The power supplies are then stressed with over-voltage values either at 1.5 x VMAX or MSV (see Figure 6). 2.4 Signal Latch-UpVLSI Design & Test Symposium (VDAT) was initiated as a workshop in 1998. However, has attained the status of a Symposium from the year 2005 due to the progressively rising participation each year by VLSI-related professionals and academia. . The superior technical paper presentations have empowered participants to acquire new directions in .

Download VTU VLSI Testing of 1st semester VLSI DESIGN AND EMBEDDED SYSTEMS with subject code 18EVE14 2018 scheme Question Papers. . VTU VLSI Testing JAN 2019 Question Paper VLSI Testing Question Papers Download VTU 18EVE14 Jan 2019 Question paper. A d v e r t i s e m e n t. 18EVE14 Question Paper.The Very Large Scale Integration (VLSI) industry has started adapting the Artificial Intelligence (AI) techniques in design automation as it provides the opportunity to transform the whole chip design methodology. It has been seen that in System-On-Chip (SoC), in order to add ML algorithms to increase its efficiency, there is a need to reduce the existing power consumption .The three significant VLSI testing methods covered in this blog are DFT (Design for Testability), BIST (Built-In Self-Test), and ATPG (Automatic Test Pattern Generation).DFT focuses on developing semiconductors that are testable, including elements and features that make testing effective. It makes defect detection and diagnosis simpler, which .

High-bandwidth memory (HBM) is a JEDEC-defined standard, dynamic random access memory (DRAM) technology that uses through-silicon vias (TSVs) to interconnect stacked DRAM die. In its first implementation, it is being integrated with a system-on-chip (SoC) logic die using 2.5D silicon interposer technology. In June 2015, AMD introduced its Fiji processor, the first HBM 2.5DVLSI Test Technology and Reliability (ET4076) 5 What is VLSI Test and reliability? • Test/Quality • Guarantee that the IC performs its function at t=0 • Conformance to specifications: time-independent • Measured in DPM (defects part per million) • Driven by defect/fault coverage & performance guard-bands • Impacts B2B relationshipVTU question paper of 18EVE14 VLSI Testing Dec - 2019 - Free download as PDF File (.pdf) or read online for free.

vlsi testing problems

vlsi testing

Resultado da 16 de nov. de 2023 · A Barbie chegou no Villa com muita alegria! 勺 Faça um orçamento agora mesmo! Fale conosco pelo WhatsApp: (71) 99700-0928 (link na bio). Rua do Beija Flor, 62, Imbuí, Salvador - BA.

vlsi testing white papers|vlsi problems and solutions